# SMARC<sup>®</sup> conga-SA5

SMARC 2.0 module based on the Intel® Atom™, Pentium™ and Celeron® Apollo Lake SoC

User's Guide

Revision 0.1 (Preliminary)

# **Revision History**

| Revision | Date (yyyy-mm-dd) | Author | Changes             |

|----------|-------------------|--------|---------------------|

| 0.1      | 2017-08-16        | AEM    | Preliminary release |

# Preface

This user's guide provides information about the components, features, connectors and BIOS Setup menus available on the conga-SA5. It is one of three documents that should be referred to when designing a SMARC<sup>®</sup> application. The other reference documents that should be used include the following:

SMARC<sup>®</sup> Design Guide 2.0 SMARC<sup>®</sup> Specification 2.0

You can find the link to these documents on the SGET website at www.sget.org

#### Disclaimer

The information contained within this user's guide, including but not limited to any product specification, is subject to change without notice.

congatec AG provides no warranty with regard to this user's guide or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. congatec AG assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the user's guide. In no event shall congatec AG be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this user's guide or any other information contained herein or the use thereof.

### **Intended Audience**

This user's guide is intended for technically qualified personnel. It is not intended for general audiences.

## Lead-Free Designs (RoHS)

All congatec AG designs are created from lead-free components and are completely RoHS compliant.

#### **Electrostatic Sensitive Device**

All congatec AG products are electrostatic sensitive devices and are packaged accordingly. Do not open or handle a congatec AG product except at an electrostatic-free workstation. Additionally, do not ship or store congatec AG products near strong electrostatic, electromagnetic, magnetic, or radioactive fields unless the device is contained within its original manufacturer's packaging. Be aware that failure to comply with these guidelines will void the congatec AG Limited Warranty.

### **Symbols**

The following symbols are used in this user's guide:

Warnings indicate conditions that, if not observed, can cause personal injury.

Cautions warn the user about how to prevent damage to hardware or loss of data.

Notes call attention to important information that should be observed.

### **Copyright Notice**

Copyright © 2017, congatec AG. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from congatec AG.

congatec AG has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied "as-is".

#### Trademarks

Product names, logos, brands, and other trademarks featured or referred to within this user's guide, or the congatec website, are the property of their respective trademark holders. These trademark holders are not affiliated with congatec AG, our products, or our website.

#### Warranty

congatec AG makes no representation, warranty or guaranty, express or implied regarding the products except its standard form of limited warranty ("Limited Warranty") per the terms and conditions of the congatec entity, which the product is delivered from. These terms and conditions can be downloaded from www.congatec.com. congatec AG may in its sole discretion modify its Limited Warranty at any time and from time to time.

The products may include software. Use of the software is subject to the terms and conditions set out in the respective owner's license agreements, which are available at www.congatec.com and/or upon request.

Beginning on the date of shipment to its direct customer and continuing for the published warranty period, congatec AG represents that the products are new and warrants that each product failing to function properly under normal use, due to a defect in materials or workmanship or due to non conformance to the agreed upon specifications, will be repaired or exchanged, at congatec's option and expense.

Customer will obtain a Return Material Authorization ("RMA") number from congatec AG prior to returning the non conforming product freight prepaid. congatec AG will pay for transporting the repaired or exchanged product to the customer.

Repaired, replaced or exchanged product will be warranted for the repair warranty period in effect as of the date the repaired, exchanged or replaced product is shipped by congatec, or the remainder of the original warranty, whichever is longer. This Limited Warranty extends to congatec's direct customer only and is not assignable or transferable.

Except as set forth in writing in the Limited Warranty, congatec makes no performance representations, warranties, or guarantees, either express or implied, oral or written, with respect to the products, including without limitation any implied warranty (a) of merchantability, (b) of fitness for a particular purpose, or (c) arising from course of performance, course of dealing, or usage of trade.

congatec AG shall in no event be liable to the end user for collateral or consequential damages of any kind. congatec shall not otherwise be liable for loss, damage or expense directly or indirectly arising from the use of the product or from any other cause. The sole and exclusive remedy against congatec, whether a claim sound in contract, warranty, tort or any other legal theory, shall be repair or replacement of the product only.

#### Certification

congatec AG is certified to DIN EN ISO 9001:2008 standard.

## **Technical Support**

congatec AG technicians and engineers are committed to providing the best possible technical support for our customers so that our products can be easily used and implemented. We request that you first visit our website at www.congatec.com for the latest documentation, utilities and drivers, which have been made available to assist you. If you still require assistance after visiting our website then contact our technical support department by email at support@congatec.com

## Terminology

| Term  | Description               |

|-------|---------------------------|

| GB    | Gigabyte                  |

| GHz   | Gigahertz                 |

| kВ    | Kilobyte                  |

| MB    | Megabyte                  |

| MTps  | Mega-transfers per second |

| Mbit  | Megabit                   |

| kHz   | Kilohertz                 |

| MHz   | Megahertz                 |

| TDP   | Thermal Design Power      |

| PCIe  | PCI Express               |

| SATA  | Serial ATA                |

| PEG   | PCI Express Graphics      |

| PCH   | Platform Controller Hub   |

| eDP   | Embedded DisplayPort      |

| DDI   | Digital Display Interface |

| HDA   | High Definition Audio     |

| N.C   | Not connected             |

| N.A   | Not available             |

| T.B.D | To be determined          |

# Contents

| 1                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.2.1                                                                    | SMARC® Concept10conga-SA5 Options Information10Options Information11                                                                                                                                                                                                                                                                                          |

| 2                                                                                      | Specifications13                                                                                                                                                                                                                                                                                                                                              |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.5<br>2.6<br>2.7                        | Feature List13Supported Operating Systems14Mechanical Dimensions14Supply Voltage Standard Power15Electrical Characteristics15Rise Time15Power Consumption16Supply Voltage Battery Power17Environmental Specifications18                                                                                                                                       |

| 3                                                                                      | Block Diagram19                                                                                                                                                                                                                                                                                                                                               |

| 4                                                                                      | Cooling Solutions                                                                                                                                                                                                                                                                                                                                             |

| 4.1<br>4.2                                                                             | CSP Dimensions                                                                                                                                                                                                                                                                                                                                                |

| 5                                                                                      | Connector Rows25                                                                                                                                                                                                                                                                                                                                              |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | Display Interfaces.       25         LVDS.       25         HDMI.       26         DP ++       26         PCI Express™.       26         Gigabit Ethernet       27         Serial ATA™ (SATA).       27         Universal Serial Bus (USB)       27         SD Card.       28         Audio (HDA / I²S)       29         UART.       29         GPIO       29 |

|                                                                                        |                                                                                                                                                                                                                                                                                                                                                               |

| 5.10<br>5.10.1<br>5.10.2<br>5.10.3<br>5.11                                                                                                            | Communication Buses<br>SPI<br>I2C<br>I2S<br>Power Control                                                                                                                                                                                                                                                                                                                                                                                                        | . 29<br>. 30<br>. 30                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 6                                                                                                                                                     | Additional Features                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                                                             |

| 6.1<br>6.2<br>6.2.1.1<br>6.2.1.2<br>6.2.1.3<br>6.2.1.4<br>6.2.1.5<br>6.2.1.6<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.4<br>6.5<br>6.6 | Optional Onboard Interfaces<br>Standard Onboard Interfaces<br>congatec Board Controller (cBC)<br>Board Information<br>General Purpose Input/Output<br>Fan Control<br>Power Loss Control<br>Watchdog<br>I <sup>2</sup> C Bus<br>OEM BIOS Customization<br>OEM Default Settings<br>OEM Default Settings<br>OEM Dost Logo<br>OEM POST Logo<br>OEM BIOS Code/Data<br>OEM DXE Driver<br>congatec Battery Management Interface<br>API Support (CGOS)<br>Suspend to Ram | .33<br>.33<br>.33<br>.34<br>.34<br>.34<br>.35<br>.35<br>.35<br>.35<br>.35<br>.36<br>.36<br>.37 |

| 7                                                                                                                                                     | conga Tech Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .38                                                                                            |

| 7.1<br>7.1.1<br>7.1.1.1<br>7.1.1.2<br>7.1.1.3<br>7.2<br>7.3                                                                                           | Intel <sup>®</sup> Apollo Lake SoC Features<br>Processor Core<br>Intel Virtualization Technology<br>AHCI<br>Thermal Management<br>ACPI Suspend Modes and Resume Events<br>USB Port Mapping                                                                                                                                                                                                                                                                       | . 38<br>. 38<br>. 39<br>. 39<br>. 40<br>. 41                                                   |

| 8                                                                                                                                                     | Signal Descriptions and Pinout Tables                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                                                             |

| 9  | System Resources        | - |

|----|-------------------------|---|

| 10 | BIOS Setup Description  |   |

| 11 | Industry Specifications | ) |

# List of Tables

| Table 1  | conga-SA5 (Commercial variants)             | 11 |

|----------|---------------------------------------------|----|

| Table 2  | conga-SA5 (Industrial variants)             | 12 |

| Table 3  | Feature Summary                             | 13 |

| Table 4  | Measurement Description                     | 16 |

| Table 5  | Power Consumption Values                    | 17 |

| Table 6  | CMOS Battery Power Consumption              |    |

| Table 7  | Display Combination                         |    |

| Table 8  | Possible USB Port Mapping                   |    |

| Table 9  | Wake Events                                 | 40 |

| Table 10 | Signal Tables Terminology Descriptions      | 42 |

| Table 11 | SMARC Edge Finger Pinout                    | 43 |

| Table 12 | LVDS Signal Description                     | 48 |

| Table 13 | HDMI Signal Descriptions                    |    |

| Table 14 | DisplayPort++                               | 52 |

| Table 15 | MIPI CSI 2.0/3.0                            | 52 |

| Table 16 | SDIO Signal Descriptions                    | 53 |

| Table 17 | SPIO Signal Descriptions                    | 54 |

| Table 18 | eSPI/SPI1 Signal Descriptions               | 54 |

| Table 19 | I2S Signal Descriptions                     | 55 |

| Table 20 | HDA / I2S Signal Descriptions               | 55 |

| Table 21 | I2C Signal Descriptions                     | 55 |

| Table 22 | Asynchronous Serial Port Signal Description | 56 |

| Table 23 | USB Pinout Description                      | 56 |

| Table 24 | PCIe Signal Description                     | 57 |

| Table 25 | SATA Signal Description                     | 58 |

| Table 26 | Gigabit Ethernet Signal Description         | 59 |

| Table 27 | Watchdog Signal Description                 | 59 |

| Table 28 | GPIO Signal Description                     | 60 |

| Table 29 | Management Pins Signal Description          | 60 |

| Table 30 | Boot Select Signal Description              | 61 |

| Table 31 | Power and GND Signal Descriptions           | 63 |

| Table 32 | References                                  | 66 |

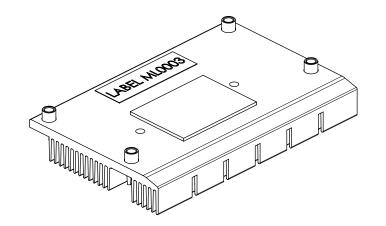

# 1 Introduction

## 1.1 SMARC<sup>®</sup> Concept

The Standardization Group for Embedded Technologies e.V (SGET) defined the SMARC standard for small form factor computer modules that target applications with ultra low power, low cost and high performance. The SMARC connector and interfaces are optimized for high-speed communication, and are suitable for ARM SoCs and low power x86 SoCs.

The SMARC standard bridges the gap between the COM Express standard and the Qseven standard by offering most of the interfaces defined in the COM Express specification at a lower power. With a footprint of 82 mm x 50 mm or 82 mm x 80 mm, the SMARC standard promotes the design of highly integrated, energy efficient systems.

Due to its small size and lower power demands, PC appliance designers can design low cost devices as well as explore a huge variety of product development options—from compact space-saving designs to fully functional systems. This solution allows scalability, product diversification and faster time to market.

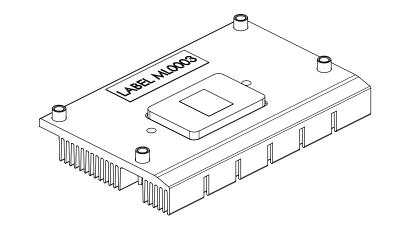

### 1.2 conga-SA5 Options Information

The conga-SA5 is designed based on the SMARC 2.0 Specification. The conga-SA5 features the Intel Atom, Pentium and Celeron Apollo Lake SoCs. With maximum 12 W TDP, the conga-SA5 offers Ultra Low Power boards with high computing performance and outstanding graphics. Additionally, the conga-SA5 supports quad channel LPDDR4 memory with up 8 GB capacity and data rates up to 2400 MTps, multiple I/O interfaces, up to three independent displays and various congatec embedded features.

By offering most of the functional requirement for any SMARC application, the conga-SA5 provides manufacturers and developers with a platform to jump-start the development of systems and applications based on SMARC specification. Its features and capabilities make it an ideal platform for designing compact, energy-efficient, performance-oriented embedded systems.

## 1.2.1 Options Information

The conga-SA5 is available in eight variants (five commercial and three industrial). The table below shows the different configurations available.

| Part-No               |              | 050000                             | 050001                             | 050002                             | 050022                                         | 050023                                         |  |

|-----------------------|--------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------------------|------------------------------------------------|--|

| Processor             |              | Intel® Atom™ x7-E3950,             | Intel® Atom™ x5-E3940,             | Intel <sup>®</sup> Atom™ x5-E3930, | Intel <sup>®</sup> Celeron <sup>®</sup> N3350, | Intel <sup>®</sup> Pentium <sup>®</sup> N4200, |  |

|                       |              | 1.6 GHz, Quad Core                 | 1.6 GHz, Quad Core                 | 1.3 GHz, Dual Core                 | 1.1 GHz, Dual Core                             | 1.1 GHz, Quad Core                             |  |

| Burst Freq            |              | 2.0 GHz                            | 1.8 GHz                            | 1.8 GHz                            | 2.4 GHz                                        | 2.5 GHz                                        |  |

| L2 Cache              |              | 2 MB                               | 2 MB                               | 2 MB                               | 2 MB                                           | 2 MB                                           |  |

| Graphics E            | Ingine       | Intel <sup>®</sup> HD Graphics 505 | Intel <sup>®</sup> HD Graphics 500 | Intel <sup>®</sup> HD Graphics 500 | Intel <sup>®</sup> HD Graphics 500             | Intel <sup>®</sup> HD Graphics 505             |  |

| GFX Base/             | 'Burst Freq. | 500 / 650 MHz                      | 400 / 600 MHz                      | 400 / 550 MHz                      | 200 / 650                                      | 200 / 750                                      |  |

| Onboard N<br>(LPDDR4) | Nemory       | 8 GB, 2400 MTps<br>quad channel    | 4 GB, 2133 MTps<br>quad channel    | 2 GB 2133 MTps<br>dual channel     | 4 GB 2400 MTps<br>quad channel                 | 8 GB 2400 MTps<br>quad channel                 |  |

| PCle                  |              | 2x Gen2                            | 2x Gen2                            | 2x Gen2                            | 2x Gen2                                        | 2x Gen2                                        |  |

| Ethernet              |              | 2x i211                            | 2x i211                            | 2x i211                            | 2x i211                                        | 2x i211                                        |  |

| Display               | LVDS         | Single/Dual 18/24bit               | Single/Dual 18/24bit               | Single/Dual 18/24bit               | Single/Dual 18/24bit                           | Single/Dual 18/24bit                           |  |

| Interfaces            | DP++         | 1x DP++                            | 1x DP++                            | 1x DP++                            | 1x DP++                                        | 1x DP++                                        |  |

|                       | HDMI         | 1x native HDMI                     | 1x native HDMI                     | 1x native HDMI                     | 1x native HDMI                                 | 1x native HDMI                                 |  |

| USB ports             |              | 4x USB 2.0<br>2x USB 3.0/2.0                   | 4x USB 2.0<br>2x USB 3.0/2.0                   |  |

| eMMC                  |              | 32 GB, MLC                         | 32 GB, MLC                         | 16 GB, MLC                         | 32 GB, MLC                                     | 32 GB, MLC                                     |  |

| Wifi/BT M             | odule        | N.A                                | N.A                                | N.A                                | N.A                                            | N.A                                            |  |

| Onboard 1             | ГРМ          | N.A                                | N.A                                | N.A                                | N.A                                            | N.A                                            |  |

| SD Card               |              | 1x 4-bit                           | 1x 4-bit                           | 1x 4-bit                           | 1x 4-bit                                       | 1x 4-bit                                       |  |

| Max. TDP              |              | 12 W                               | 9.5 W                              | 6.5 W                              | 6 W                                            | 6 W                                            |  |

#### Table 1 conga-SA5 (Commercial variants)

| Part-No     |             | 050010                             | 050011                             | 050012                             |

|-------------|-------------|------------------------------------|------------------------------------|------------------------------------|

| Processor   |             | Intel <sup>®</sup> Atom™ x7-E3950, | Intel <sup>®</sup> Atom™ x5-E3940, | Intel® Atom™ x5-E3930,             |

|             |             | 1.6 GHz, Quad Core                 | 1.6 GHz, Quad Core                 | 1.3 GHz, Dual Core                 |

| Burst Freq. |             | 2.0 GHz                            | 1.8 GHz                            | 1.8 GHz                            |

| L2 Cache    |             | 2 MB                               | 2 MB                               | 1 MB                               |

| Graphics E  | ingine      | Intel <sup>®</sup> HD Graphics 505 | Intel <sup>®</sup> HD Graphics 500 | Intel <sup>®</sup> HD Graphics 500 |

| GFX Base/   | Burst Freq. | 500 / 650 MHz                      | 400 / 600 MHz                      | 400 / 550 MHz                      |

| Onboard N   | /lemory     | 8 GB, 2400 MTps                    | 4 GB, 2133 MTps                    | 2 GB 2133 MTps                     |

| (LPDDR4)    |             | quad channel                       | quad channel                       | dual channel                       |

| PCle        |             | 2x Gen2                            | 2x Gen2                            | 2x Gen2                            |

| Ethernet    |             | 2x i210                            | 2x i210                            | 2x i210                            |

| Display     | LVDS        | Single/Dual 18/24bit               | Single/Dual 18/24bit               | Single/Dual 18/24bit               |

| Interfaces  | DP++        | 1x DP++                            | 1x DP++                            | 1x DP++                            |

|             | HDMI        | 1x native HDMI                     | 1x native HDMI                     | 1x native HDMI                     |

| USB ports   |             | 4x USB 2.0                         | 4x USB 2.0                         | 4x USB 2.0                         |

|             |             | 2x USB 3.0/2.0                     | 2x USB 3.0/2.0                     | 2x USB 3.0/2.0                     |

| eMMC        |             | 32 GB, MLC                         | 32 GB, MLC                         | 16 GB, MLC                         |

| Wifi/BT Mo  | odule       | Optional                           | Optional                           | Optional                           |

| Onboard T   | PM          | Optional                           | Optional                           | Optional                           |

| SD Card     |             | 1x 4-bit                           | 1x 4-bit                           | 1x 4-bit                           |

| Max. TDP    |             | 12 W                               | 9.5 W                              | 6.5 W                              |

#### Table 2conga-SA5 (Industrial variants)

# 2 Specifications

## 2.1 Feature List

#### Table 3Feature Summary

| Form Factor                  | SMARC <sup>®</sup> form factor specification, revision 2.0 (82 mm x 50 mm)                                                                                                                                                                                               |                                                                                                                                                                                        |  |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SoC                          | Intel® Atom™, Pentium® and Celeron SoCs                                                                                                                                                                                                                                  |                                                                                                                                                                                        |  |  |  |  |  |

| Memory                       | Onboard non-ECC LPDDR4 memory. Supports <ul> <li>Data rates up to 2400 MTps</li> <li>Up to 8 GB capacity</li> </ul>                                                                                                                                                      |                                                                                                                                                                                        |  |  |  |  |  |

| congatec Board<br>Controller | Multi-stage watchdog, non-volatile user data storage, manufacturing and board information, board statistics, hardware monitoring, fan control, I2C bus, Power loss control                                                                                               |                                                                                                                                                                                        |  |  |  |  |  |

| Chipset                      | Integrated in the SoC                                                                                                                                                                                                                                                    |                                                                                                                                                                                        |  |  |  |  |  |

| Audio                        | High Definition Audio interface with support for multiple codecs                                                                                                                                                                                                         |                                                                                                                                                                                        |  |  |  |  |  |

| Ethernet                     | 2x Gigabit Ethernet via Intel® i210 and i211 controllers.                                                                                                                                                                                                                |                                                                                                                                                                                        |  |  |  |  |  |

| Graphics Options             | <ul> <li>Next Generation Intel® HD (500/505). Supports:</li> <li>API (DirectX 12, OpenGL 4.3, OpenCL 2.0, OpenGL ES 3.0</li> <li>Intel® QuickSync &amp; Clear Video Technology HD (hardware</li> <li>Up to 3 independent displays (must be two DDI's and one)</li> </ul> | accelerated video decode/encode/processing/transcode)                                                                                                                                  |  |  |  |  |  |

|                              | 1x LVDS (dual channel)<br>1x DP++ (DDI0)<br>1x HDMI (native)<br>2x MIPI-CSI (x4 and x2 lanes)<br><b>Optional Interface (assembly option)</b> :<br>- 1x eDP 1.4 *1<br>- 1x DSI *2<br>- 1x DP++ (DDI1) *3                                                                  | NOTE:<br>*1 With this option, LVDS is not supported<br>*2 With this option, dual LVDS channel is not supported.<br>*3 With this option, native HDMI is not supported.                  |  |  |  |  |  |

| Peripheral<br>Interfaces     | 1x SATA® III<br>Up to 4x PCIe® Gen2 ports<br>USB Interfaces<br>- 4x USB 2.0<br>- 2x USB 3.0/2.0<br>4x UART (two with handshake signals)<br>1x SD/SDIO<br>eMMC 5.0 (up to 64 GB)                                                                                          | Buses<br>- 2x I <sup>2</sup> C<br>- up to 2x I <sup>2</sup> S<br>- 2x SPI (eSPI and SPI)<br><b>Optional Interface (assembly option)</b> :<br>- M.2 1216 Wi-fi module<br>- TPM 2.0 chip |  |  |  |  |  |

| BIOS                         | AMI Aptio® UEFI 5.x firmware, 8 MB serial SPI with congatec Em                                                                                                                                                                                                           | bedded BIOS features.                                                                                                                                                                  |  |  |  |  |  |

| Power Mgmt.                  | ACPI 5.0 compliant with battery support. Also supports Suspend                                                                                                                                                                                                           | to RAM (S3)                                                                                                                                                                            |  |  |  |  |  |

#### • Note

Some of the features mentioned in the above Feature Summary are optional. Check the article number of your module and compare it to the option information list on page 11 to determine what options are available on your particular module.

# 2.2 Supported Operating Systems

The conga-SA5 supports the following operating systems.

- Microsoft<sup>®</sup> Windows<sup>®</sup> 10 IoT Enterprise

- Microsoft<sup>®</sup> Windows<sup>®</sup> IoT Core

- Microsoft<sup>®</sup> Windows<sup>®</sup> 10

- Linux 3.x / 4.x

- Android 6.x

- Yocto 2.x

- Note

To install Windows<sup>®</sup> 10, you require a minimum storage capacity of 20 GB. We will not offer installation support for systems with less than 20 GB storage space.

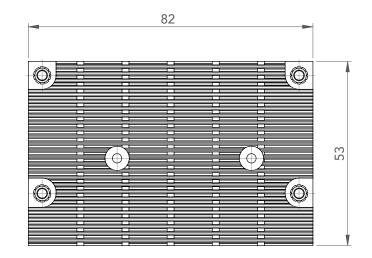

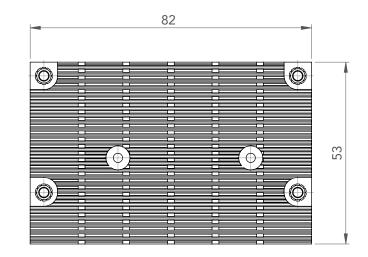

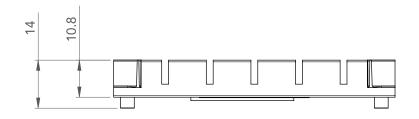

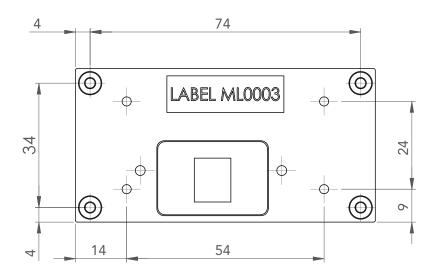

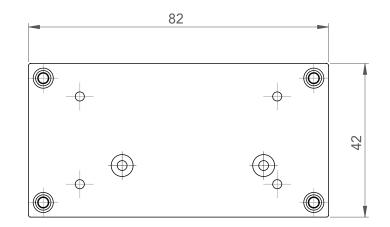

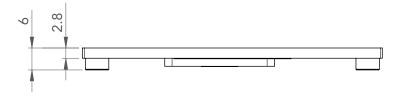

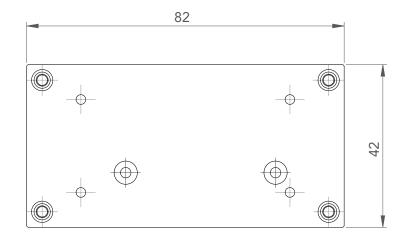

## 2.3 Mechanical Dimensions

• 82.0 mm x 50.0 mm

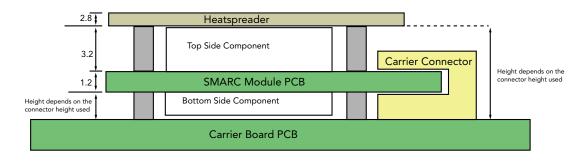

The height of the module, the heatspreader and the stack is shown below:

SA50m01

# 2.4 Supply Voltage Standard Power

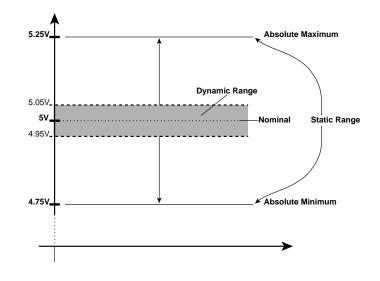

• 4.75 V – 5.25 V

### 2.4.1 Electrical Characteristics

| Characteristics |         |      | Min. | Тур. | Max. | Units            | Comment |

|-----------------|---------|------|------|------|------|------------------|---------|

| 5V              | Voltage | ± 5% | 4.75 | 5.00 | 5.25 | Vdc              |         |

|                 | Ripple  |      | -    | -    | ± 50 | mV <sub>PP</sub> | 0-20MHz |

|                 | Current |      |      |      |      |                  |         |

### 2.4.2 Rise Time

TBD

## 2.5 Power Consumption

The power consumption values were measured with the following setup:

- conga-SA5 COM

- conga-SEVA (supplied with two different power supplies at the same time)

- conga-SA5 cooling solution

- Microsoft Windows 10 (64 bit)

#### Table 4 Measurement Description

The power consumption values were recorded during the following system states:

| System State      | Description                                                                                                                                                                | Comment                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| S0: Minimum value | Lowest frequency mode (LFM) with minimum core voltage during desktop idle.                                                                                                 |                                                                                                                                          |

| S0: Maximum value | Highest frequency mode (HFM/Turbo Boost).                                                                                                                                  | The CPU was stressed to its maximum frequency.                                                                                           |

| S0: Peak value    | Highest power spike during the measurement of "S0: Maximum value".<br>This state shows the peak value over a short period of time (worst case<br>power consumption value). | Consider this value when designing the system's power supply to<br>ensure that sufficient power is supplied during worst case scenarios. |

| S3                | COM is powered by VCC_5V, while in Suspend to RAM state.                                                                                                                   |                                                                                                                                          |

| S5                | COM is powered by VCC_5V, while in Soft-Off state                                                                                                                          |                                                                                                                                          |

#### Note

The peripherals did not influence the measured values because they were powered externally.

#### Table 5Power Consumption Values

The tables below provide additional information about the power consumption data for each of the conga-SA5 variants offered. The values are recorded at various operating mode.

| Part   | Memory | H.W  | BIOS | OS (64 bit) | CPU                                           |       |                   |         | Power ( | Consumpti | on (W) |     |

|--------|--------|------|------|-------------|-----------------------------------------------|-------|-------------------|---------|---------|-----------|--------|-----|

| No.    | Size   | Rev. | Rev. |             | Variant                                       | Cores | Freq. /Max. Turbo | S0: Min | S0: Max | S0: Peak  | S3     | S5  |

| 050000 | 8 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3950             | 4     | 1.6 / 2.0 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050001 | 4 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3940             | 4     | 1.6 / 1.8 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050002 | 2 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3930             | 2     | 1.3 / 1.8 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050010 | 8 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3950             | 4     | 1.6 / 2.0 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050011 | 4 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3940             | 4     | 1.6 / 1.8 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050012 | 2 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3930             | 2     | 1.3 / 1.8 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050022 | 4 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Celeron <sup>®</sup> N3350 | 2     | 1.1 / 2.3 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050023 | 8 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Pentium <sup>®</sup> N4200 | 2     | 1.1 / 2.5 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

| 050030 | 8 GB   | A.0  | R000 | Windows 10  | Intel <sup>®</sup> Atom™ x7-E3950             | 4     | 1.6 / 2.0 GHz     | TBD     | TBD     | TBD       | TBD    | TBD |

## 2.6 Supply Voltage Battery Power

#### Table 6CMOS Battery Power Consumption

| RTC @ | Voltage | Current |

|-------|---------|---------|

| -10°C | 3V DC   | TBD µA  |

| 20°C  | 3V DC   | TBD µA  |

| 70°C  | 3V DC   | TBD µA  |

#### Note

- 1. Do not use the CMOS battery power consumption values listed above to calculate CMOS battery lifetime.

- 2. Measure the CMOS battery power consumption in your customer specific application in worst case conditions (for example, during high temperature and high battery voltage).

- 3. Consider the self-discharge of the battery when calculating the lifetime of the CMOS battery. For more information, refer to application note AN9\_RTC\_Battery\_Lifetime.pdf on congatec AG website at www.congatec.com/support/application-notes.

# 2.7 Environmental Specifications

| Temperature (commercial variants) | Operation: 0° to 60°C   | Storage: -20° to +80°C |

|-----------------------------------|-------------------------|------------------------|

| Temperature (industrial variants) | Operation: -40° to 85°C | Storage: -45° to +85°C |

| Humidity                          | Operation: 10% to 90%   | Storage: 5% to 95%     |

The above operating temperatures must be strictly adhered to at all times. When using a congatec heatspreader, the maximum operating temperature refers to any measurable spot on the heatspreader's surface.

Humidity specifications are for non-condensing conditions.

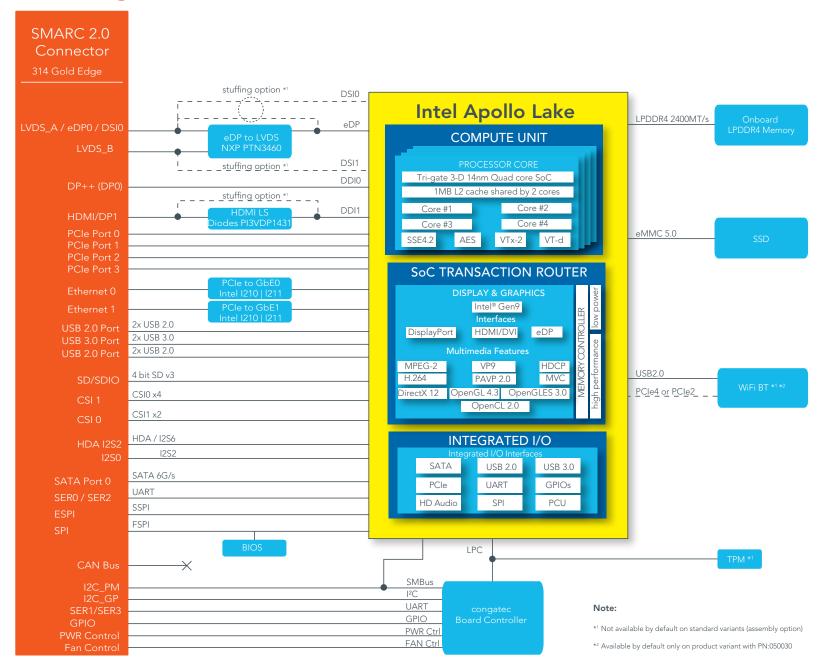

# 3 Block Diagram

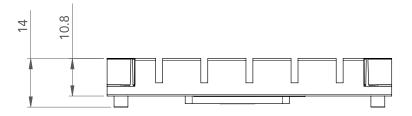

# **Cooling Solutions**

congatec AG offers the following cooling solutions for the conga-SA5 commercial and industrial variants:

- Passive cooling solution (CSP)

- Heatspreader

The heatspreader acts as a thermal coupling device to the module and is thermally coupled to the CPU via a thermal gap filler. On some modules, it may also be thermally coupled to other heat generating components with the use of additional thermal gap fillers.

Although the heatspreader is the thermal interface where most of the heat generated by the module is dissipated, it is not to be considered as a heatsink. It has been designed as a thermal interface between the module and the application specific thermal solution. The application specific thermal solution may use heatsinks with fans, and/or heat pipes, which can be attached to the heatspreader. Some thermal solutions may also require that the heatspreader is attached directly to the systems chassis thereby using the whole chassis as a heat dissipater.

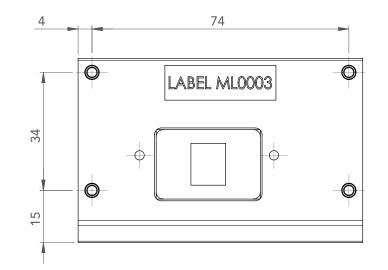

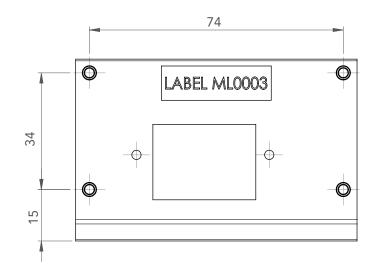

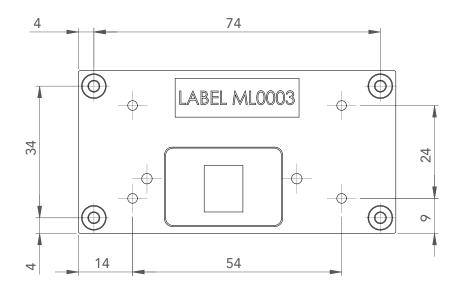

The dimensions of the cooling solutions are shown below. All measurements are in millimeters. The mechanical system assembly mounting shall follow the valid DIN/ISO specifications. The recommended maximum torgue specification for all screws is 0.3 Nm.

#### >Note

The gap pad material used on all congatec heatspreaders contains silicon oil that can seep out over time depending on the environmental conditions it is subjected to. For more information about this subject, contact your local congatec sales representative and request the gap pad material manufacturer's specification.

## Caution

The congatec heatspreaders/cooling solutions are tested only within the commercial temperature range of 0° to 60°C. Therefore, if your application that features a congatec heatspreader/cooling solution operates outside this temperature range, ensure the correct operating temperature of the module is maintained at all times. This may require additional cooling components for your final application's thermal solution.

For adequate heat dissipation, use the mounting holes on the cooling solution to attach it to the module. Apply thread-locking fluid on the screws if the cooling solution is used in a high shock and/or vibration environment. To prevent the standoff from stripping or cross-threading, use threaded carrier board standoffs to mount non-threaded cooling solutions.

For applications that require vertically-mounted cooling solution, use only coolers that secure the thermal stacks with fixing post. Without the fixing post feature, the thermal stacks may move.

Also, do not exceed the maximum torque specified for the screws. Doing so may damage the module or the carrier board or both.

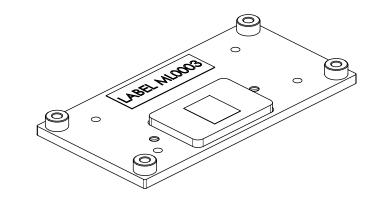

# 4.1 CSP Dimensions

#### **Commercial Variant**

Industrial Variant

# 4.2 Heatspreader Dimensions

#### **Commercial Variant**

Industrial Variant

# 5 Connector Rows

The conga-SA5 has 314 edge fingers that mate with the MXM3 connector located on the carrier board. This connector is able to interface the signals on the conga-SA5 with the carrier board peripherals.

# 5.1 Display Interfaces

The conga-SA5 offers the following display interfaces:

- dual channel LVDS

- native HDMI

- dual mode DisplayPort (DP++)

The display combination is shown below:

| Table 7 | <b>Display Combination</b> |

|---------|----------------------------|

|---------|----------------------------|

|          | Display 1 |                  | Display 2 |                  | Display 3         |                                                                                                                                     |

|----------|-----------|------------------|-----------|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|          | External  | Max. Resolution  | External  | Max. Resolution  | Internal/External | Max. Resolution                                                                                                                     |

| Default  | DP++      | 4096x2160 @ 60Hz | HDMI      | 3840x2160 @ 30Hz | LVDS              | 1920x1200 @ 60Hz (dual mode)                                                                                                        |

| Option 1 | DP++      | 4096x2160 @ 60Hz | HDMI      | 3840x2160 @ 30Hz | eDP/DSI           | eDP: 3840x2160 @ 60 Hz<br>DSI: 1920x1200 @ 60 Hz (1 x4 lane) or 2560x1600 @ 60 Hz (2 x4 lane)                                       |

| Option 2 | DP++      | 4096x2160 @ 60Hz | DP++      | 4096x2160 @ 60Hz | LVDS/DSI/eDP      | LVDS: 1920x1200 @ 60Hz (dual mode)<br>eDP: 3840x2160 @ 60 Hz<br>DSI: 1920x1200 @ 60 Hz (1 x4 lane) or 2560x1600 @ 60 Hz (2 x4 lane) |

## 5.1.1 LVDS

congatec

The conga-SA5 offers an LVDS interface on the edge finger. The interface supports:

- single or dual channel LVDS (color depths of 18 bpp or 24 bpp)

- integrated flat panel interface with clock frequency up to 112 MHz

- VESA and OpenLDI LVDS color mappings

- automatic panel detection via Embedded Panel Interface based on VESA EDIDTM 1.3

- resolution up to 1920x1200 in dual LVDS bus mode

#### Note

- 1. LVDS channel A (first channel) supports an optional eDP or MIPI DSI interface (assembly option).

- 2. Variants with optional eDP or MIPI-DSI interface do not support LVDS interface

- 3. Only one MIPI-DSI panel is supported (maximum of two channels, with up to four lanes each)

### 5.1.2 HDMI

The conga-SA5 offers a native HDMI interface. The interface supports:

- HDMI 1.4b specification

- resolutions up to 3840x2160 @ 30 Hz

## Note

- 1. The HDMI interface supports an optional dual mode DisplayPort interface (assembly option).

- 2. Variants with optional dual mode DisplayPort do not support native HDMI voltage levels.

## 5.1.3 DP ++

The conga-SA5 offers a dual mode DisplayPort (DP++). The interface supports:

- DisplayPort 1.2 specification

- resolutions up to 4096x2160 @ 60 Hz

# 5.2 PCI Express™

The conga-SA5 offers up to 4 PCI Express™ lanes. The lanes support:

- up to 5 GT/s (Gen 2) speed

- a 4 x1 link configuration (default)

- optional 1 x4 or 2 x2 or 1 x2 + 2 x1 \*1 link configuration (require customized BIOS firmware)

- lane polarity inversion

Note

<sup>\*1</sup> Possible with an assembly option.

# 5.3 Gigabit Ethernet

The conga-SA5 offers two Gigabit Ethernet interfaces— via Intel<sup>®</sup> i210 and i211 controllers. The interfaces support full-duplex operation at 10/100/1000 Mbps and half-duplex operation at 10/100 Mbps.

## 5.4 Serial ATA™ (SATA)

The conga-SA5 offers one SATA interface on the edge finger. The interface supports:

- SATA specification 3.2

- independent DMA operation

- data transfer rates up to 6.0 Gb/s

- AHCI mode using memory space

#### Note

The interface does not support legacy mode using I/O space.

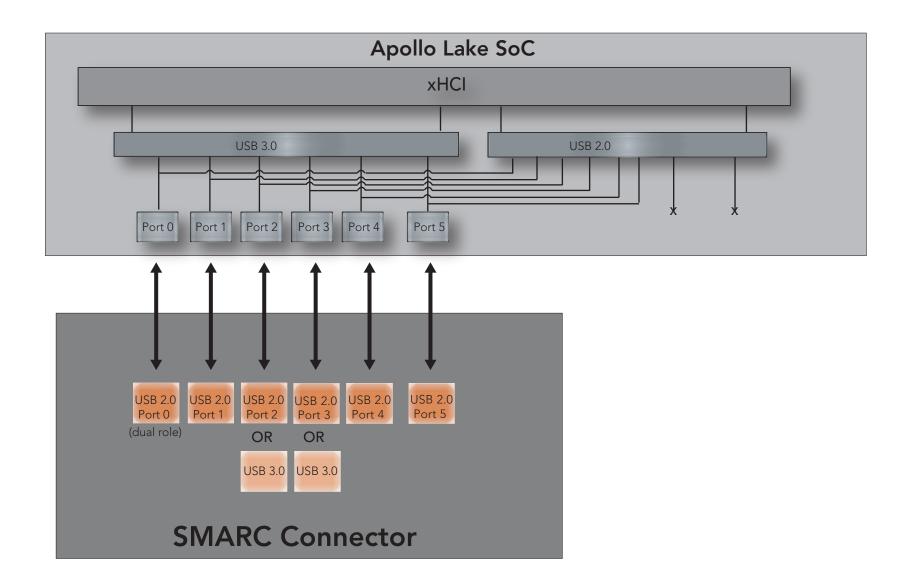

# 5.5 Universal Serial Bus (USB)

The conga-SA5 offers the following USB interfaces:

- four USB 2.0 with support for:

- USB 1.1 and 2.0 specifications

- up to 480 Mbps data transfer

- high-speed, full-speed and low-speed signalling

- additional two ports if SuperSpeed ports are not implemented

- two USB 3.0/2.0 with support for:

- USB 3.0 specification

- up to 5 Gbps data transfer

- SuperSpeed, high-speed, full-speed and low-speed signalling

- optional dual role support on USB port 3 (assembly option)

Table 8Possible USB Port Mapping

|          | USB 2.0   |           | USB 3.0/2.0 |           |

|----------|-----------|-----------|-------------|-----------|

|          | Host Only | Dual Role | Host Only   | Dual Role |

| Default  | 3 ports   | 1 port    | 2 port      | -         |

| Option 1 | 4 ports   | -         | 1 port      | 1 port    |

| Option 2 | 4 ports   | -         | 2 ports     | -         |

| Option 3 | 6 ports   | -         | -           | -         |

Note

For USB 3.0 support on your carrier board, pair USB 2.0 port 2 or 3 or both with the SuperSpeed signals.

# 5.6 SD Card

The conga-SA5 offers a 4-bit SD interface on the edge finger. The interface supports:

- SD Memory Card Specification 3.01

- SD 3.01 @ 1.8 V or @ 3.3 V signaling

- up to 200 MHz clock frequency

- up to 104 MBps data rates with four parallel data lines

- 1-bit and 4-bit transfer mode

- card insertion and removal detection

Note

The SD card interface supports only storage devices.

## 5.7 Audio (HDA / I<sup>2</sup>S)

The conga-SA5 offers the following audio interfaces:

- up to two I<sup>2</sup>S interfaces (I<sup>2</sup>S0 and I<sup>2</sup>S2)

- up to one HDA interface (shares pins with  $I^2S2$ )

#### Note

The conga-SA5 does not support GPIO functionality on GPIO4 if HDA interface is implemented.

# 5.8 UART

The conga-SA5 offers four UART interfaces:

- two UART interfaces with handshake signals (connected to the CPU)

- two legacy compatible UART interfaces without handshake signals (connected to the congatec Board Controller)

# 5.9 GPIO

The conga-SA5 offers five non-multiplexed GPIOs (port 7 - port 11) by default. The GPIOs are controlled by the congatec Board controller.

# 5.10 Communication Buses

The conga-SA5 offers the following communication buses:

- SPI

- I2C

- I2S

# 5.10.1 SPI

The conga-SA5 offers two SPI interfaces:

- eSPI/SPI1 for general purpose SPI devices

- SPIO for on-module or carrier board flash device

### 5.10.2 I2C

The conga-SA5 offers two I2C interfaces:

- general purpose I2C

- power management I2C

These interfaces are implemented through the congatec board controller and accessed through the congatec CGOS driver and API. The controller provides a fast-mode multi-master I<sup>2</sup>C bus that has maximum I<sup>2</sup>C bandwidth.

## 5.10.3 I2S

The conga-SA5 offers two I2S interfaces:

- I2S0

- I2S2 (multiplexed with HDA signals for digital audio interfaces)

## 5.11 Power Control

The conga-SA5 operates only with 5 V input voltage. Its power-up sequence is described below:

- 1. The 5 V input voltage (VDD\_IN) supplied to the carrier board powers the conga-SA5 first.

- 2. The conga-SA5 enables its power circuits if the VIN\_PWR\_BAD# signal is high.

- 3. Depending on the carrier board design and configuration, the conga-SA5 detects a power button event (PWRBTN#) if implemented.

- 4. The conga-SA5 enables the carrier board power by asserting CARRIER\_PWR\_ON (SUS\_S5#) and CARRIER\_STBY# (SUS\_S3#)

- 5. The conga-SA5 releases the RESET\_OUT# and starts the boot process.

The power control signals are described below:

#### VIN\_PWR\_BAD#

When the VIN\_PWR\_BAD# signal (pin S150) is low, it indicates that the input voltage to the conga-SA5 is either not ready or out of specified range. Carrier board hardware should drive this signal low until the input power is up and stable. Releasing VIN\_PWR\_BAD# too early can cause numerous boot up problems.

#### CARRIER\_PWR\_ON

The CARRIER\_PWR\_ON signal (pin S154) is an active-high output signal. The module asserts this signal when all its power supplies are up, and subsequently enables the carrier board power supplies. This signal is equivalent to ACPI SUS\_S5# signal.

#### CARRIER\_STBY#

The CARRIER\_STBY# signal (pin S153) is an active-low output that can be used to indicate that the conga-SA5 is going into suspend state, where only power management functions and system memory are powered.

The CARRIER\_STBY# signal can also be used to disable the carrier board power that is not required during standby.

#### RESET\_IN#

The RESET\_IN# signal (pin P127) is an active-low open drain input signal from the carrier board. The signal may be used to force the module to reset or reboot.

#### RESET\_OUT#

The RESET\_OUT# signal (pin P126) is an active-low output signal from the module. The module asserts this signal during the power-up sequencing to allow the carrier board power circuits to come up. The module deasserts this signal to begin the boot-up process.

#### POWER\_BTN#

The PWRBTN# (pin P128) is an active-low open drain power button input from the carrier board. This power button signal is used to wake up or shut down the system from S5 state (soft off).

#### **Power Supply Implementation Guidelines**

The operational power source for the conga-SA5 is 5 V. The remaining necessary voltages are internally generated on the module with onboard voltage regulators.

A carrier board designer should be aware of the important information below when designing a power supply for a conga-SA5 application:

• We have noticed that on some occasions, problems occur when using a 5V power supply that produces non monotonic voltage when powered up. The problem is that some internal circuits on the module (e.g. clock-generator chips) generate their own reset signals when the supply voltage exceeds a certain voltage threshold. A voltage dip after passing this threshold may lead to these circuits becoming confused, thereby resulting in a malfunction. This problem though rare, has been observed in some mobile power supply applications. The best way to ensure that this problem is not encountered is to observe the power supply rise waveform through an oscilloscope. This will help to determine if the rise is indeed monotonic and does not have any dips. You should do this during the power supply qualification phase to ensure that the problem does not occur in the application. For more information about this issue, visit www.formfactors.org and view page 25 figure 7 of the document "ATX12V Power Supply Design Guide V2.2".

#### Inrush and Maximum Current Peaks on VDD\_IN

The maximum peak-current on the conga-SA5 VDD\_IN (5 V) power rail can be as high as 5 A for a maximum of 100 µs. You should therefore ensure the power supply and decoupling capacitors provide enough power to drive the module.

For more information about power control event signals, refer to the SMARC<sup>®</sup> specification.

# 6 Additional Features

## 6.1 Optional Onboard Interfaces

The conga-SA5 offers the following optional interfaces:

- Wi-fi/Bluetooth module

- TPM 2.0 connected via LPC bus

- Note

The conga-SA5 variant with part number 050030 features both Wi-fi/Bluetooth and TPM modules onboard.

## 6.2 Standard Onboard Interfaces

The conga-SA5 offers the following standard interfaces:

- eMMC 5.0 (SSD) with up to 32 GB capacity

- Quad or dual channel low voltage memory (LPDDR4) with up to 2400 MTps and up to 8 GB capacity

- congatec board controller

#### 6.2.1 congatec Board Controller (cBC)

The conga-SA5 is equipped with a Texas Instruments TI Stellaris microcontroller. The microcontroller plays an important role for most of the congatec BIOS features. By isolating some of the embedded features such as system monitoring or the I<sup>2</sup>C bus from the x86 core architecture, the microcontroller increases the performance and reliability of the BIOS features, even during low power mode. In addition, it ensures the congatec embedded feature set is compatible amongst all congatec modules.

Some of the features offered by the cBC are described below:

#### 6.2.1.1 Board Information

The cBC provides a rich data-set of manufacturing and board information such as serial number, EAN number, hardware and firmware revisions, and so on. It also keeps track of dynamically changing data like runtime meter and boot counter.

#### 6.2.1.2 General Purpose Input/Output

The conga-SA5 offers general purpose inputs and outputs for custom system design. These GPIOs are controlled by the cBC.

#### 6.2.1.3 Fan Control

The conga-SA5 has additional signals and functions to further improve system management. One of these signals is an output signal called PWMOUT that allows system fan control using a PWM (Pulse Width Modulation) output. Additionally, there is an input signal called TACHIN that provides the ability to monitor the system's fan RPMs (revolutions per minute). This signal must receive two pulses per revolution in order to produce an accurate reading. For this reason, a two pulse per revolution fan or similar hardware solution is recommended.

#### Note

- 1. Use a four-wire fan to generate the correct speed readout.

- 2. For the correct fan control (PWMOUT, TACHIN) implementation, see the SMARC Design Guide Specification.

- 3. PWMOUT and TACHIN share their pins with GPIO 5 and 6 respectively. The conga-SA5 does not support fan control if these pins are used for GPIO functionality.

#### 6.2.1.4 Power Loss Control

The cBC has full control of the power-up of the module and therefore can be used to specify the behavior of the system after an AC power loss condition. Supported modes are "Always On", "Remain Off" and "Last State".

#### 6.2.1.5 Watchdog

The conga-SA5 is equipped with a multi stage watchdog solution that is triggered by software. The conga-SA5 does not support external hardware triggering because the SMARC Specification does not provide support for external hardware triggering of the watchdog.

For more information, see the application note AN3\_Watchdog.pdf on the congatec AG website at www.congatec.com.

#### Note

The conga-SA5 module does not support the watchdog NMI mode.

#### 6.2.1.6 I<sup>2</sup>C Bus

The conga-SA5 supports I<sup>2</sup>C bus. See section 5.10.3 "I2C" for more information.

## 6.3 OEM BIOS Customization

The conga-SA5 is equipped with congatec Embedded BIOS, which is based on American Megatrends Inc. Aptio UEFI firmware. The congatec Embedded BIOS allows system designers to modify the BIOS. For more information about customizing the congatec Embedded BIOS, refer to the congatec System Utility user's guide CGUTLm1x.pdf on the congatec website at www.congatec.com or contact technical support.

The customizable features are described below:

#### 6.3.1 OEM Default Settings

This feature allows system designers to create and store their own BIOS default configuration. Customized BIOS development by congatec for OEM default settings is no longer necessary because customers can easily perform this configuration by themselves using the congatec system utility CGUTIL. See congatec application note AN8\_Create\_OEM\_Default\_Map.pdf on the congatec website for details on how to add OEM default settings to the congatec Embedded BIOS.

#### 6.3.2 OEM Boot Logo

This feature allows system designers to replace the standard text output displayed during POST with their own BIOS boot logo. Customized BIOS development by congatec for OEM Boot Logo is no longer necessary because customers can easily perform this configuration by themselves using the congatec system utility CGUTIL. See congatec application note AN8\_Create\_And\_Add\_Bootlogo.pdf on the congatec website for details on how to add OEM boot logo to the congatec Embedded BIOS.

#### 6.3.3 OEM POST Logo

This feature allows system designers to replace the congatec POST logo displayed in the upper left corner of the screen during BIOS POST with their own BIOS POST logo. Use the congatec system utility CGUTIL 1.5.4 or later to replace/add the OEM POST logo.

#### 6.3.4 OEM BIOS Code/Data

With the congatec embedded BIOS it is possible for system designers to add their own code to the BIOS POST process. The congatec Embedded BIOS first calls the OEM code before handing over control to the OS loader.

#### Note

The OEM BIOS code of the new UEFI based firmware is called only when the CSM (Compatibility Support Module) is enabled in the BIOS setup menu. For more information on how to add OEM code, contact congatec technical support.

#### 6.3.5 OEM DXE Driver

This feature allows designers to add their own UEFI DXE driver to the congatec embedded BIOS. Contact congatec technical support for more information on how to add an OEM DXE driver.

#### 6.4 congatec Battery Management Interface

To facilitate the development of battery powered mobile systems based on embedded modules, congatec AG defined an interface for the exchange of data between a CPU module (using an ACPI operating system) and a Smart Battery system. A system developed according to the congatec Battery Management Interface Specification can provide the battery management functions supported by an ACPI capable operating system (e.g. charge state of the battery, information about the battery, alarms/events for certain battery states, ...) without the need for any additional modifications to the system BIOS.

In addition to the ACPI-Compliant Control Method Battery mentioned above, the latest versions of the conga-SA5 BIOS and board controller firmware also support LTC1760 battery manager from Linear Technology and a battery only solution (no charger). All three battery solutions are supported on the I2C bus and the SMBus. This gives the system designer more flexibility when choosing the appropriate battery sub-system.

For more information about this subject visit the congatec website and view the following documents:

- congatec Battery Management Interface Specification

- Battery System Design Guide

- conga-SBM<sup>3</sup> User's Guide

## 6.5 API Support (CGOS)

In order to benefit from the above mentioned non-industry standard feature set, congatec provides an API that allows application software developers to easily integrate all these features into their code. The CGOS API (congatec Operating System Application Programming Interface) is the congatec proprietary API that is available for all commonly used Operating Systems such as Win32, Win64, Win CE, Linux. The architecture of the CGOS API driver provides the ability to write application software that runs unmodified on all congatec CPU modules. All the hardware related code is contained within the congatec embedded BIOS on the module. See section 1.1 of the CGOS API software developers guide, which is available on the congatec website.

## 6.6 Suspend to Ram

The Suspend to RAM feature is available on the conga-SA5.

# 7 conga Tech Notes

The conga-SA5 has some technological features that require additional explanation. The following section will give the reader a better understanding of some of these features. This information will also help to gain a better understanding of the information found in the system resources section of this user's guide as well as some of the setup nodes found in the BIOS Setup Description section.

## 7.1 Intel<sup>®</sup> Apollo Lake SoC Features

## 7.1.1 Processor Core

The SoC features Dual or Quad Out-of-Order Execution processor cores. The cores are grouped into Dual-Core modules with each module sharing a 1 MB L2 cache (512 KB per core). Some of the features supported by the core are:

- Intel 64 architecture

- Intel Streaming SIMD Extensions

- Support for Intel VTx-2 and VT-d

- Thermal management support vial Intel Thermal Monitor

- Uses Power Aware Interrupt Routing

- Uses 14 nm process technology

#### Note

Intel Hyper-Threading technology is not supported (four cores execute four threads)

#### 7.1.1.1 Intel Virtualization Technology

Intel<sup>®</sup> Virtualization Technology (Intel<sup>®</sup> VT) makes a single system appear as multiple independent systems to software. This allows multiple, independent operating systems to run simultaneously on a single system. Intel<sup>®</sup> VT comprises technology components to support virtualization of platforms based on Intel architecture microprocessors and chipsets. Intel<sup>®</sup> Virtualization Technology for IA-32, Intel<sup>®</sup> 64 and Intel<sup>®</sup> Architecture Intel<sup>®</sup> VT-x) added hardware support in the processor to improve the virtualization performance and robustness.

## Note

congatec does not offer virtual machine monitor (VMM) software. All VMM software support questions and queries should be directed to the VMM software vendor and not congatec technical support.

### 7.1.1.2 AHCI

The SoC provides hardware support for Advanced Host Controller Interface (AHCI), a programming interface for SATA host controllers. Platforms supporting AHCI may take advantage of performance features such as no master/slave designation for SATA devices (each device is treated as a master) and hardware-assisted native command queuing. AHCI also provides usability enhancements such as Hot-Plug.

#### 7.1.1.3 Thermal Management

ACPI is responsible for allowing the operating system to play an important part in the system's thermal management. This results in the operating system having the ability to take control of the operating environment by implementing cooling decisions according to the demands put on the CPU by the application.

The conga-SA5 ACPI thermal solution offers two different cooling policies.

#### Passive Cooling

When the temperature in the thermal zone must be reduced, the operating system can decrease the power consumption of the processor by throttling the processor clock. One of the advantages of this cooling policy is that passive cooling devices (in this case the processor) do not produce any noise. Use the "passive cooling trip point" setup node in the BIOS setup program to determine the temperature threshold that the operating system will use to start or stop the passive cooling procedure.

#### Critical Trip Point

If the temperature in the thermal zone reaches a critical point then the operating system will perform a system shut down in an orderly fashion in order to ensure that there is no damage done to the system as result of high temperatures. Use the "critical trip point" setup node in the BIOS setup program to determine the temperature threshold that the operating system will use to shut down the system.

## Note

The end user must determine the cooling preferences for the system by using the setup nodes in the BIOS setup program to establish the appropriate trip points.

If passive cooling is activated and the processor temperature is above the trip point the processor clock is throttled. See section 12 of the ACPI Specification 2.0 C for more information about passive cooling.

## 7.2 ACPI Suspend Modes and Resume Events

The conga-SA5 BIOS supports S3 (Suspend to RAM). The BIOS does not support S4 (Suspend to Disk) even though the following operating systems support it (S4\_OS = Hibernate):

• Windows 10 and Linux

For more information about ACPI, see section 10.4.5 "ACPI Configuration Submenu".

#### Table 9 Wake Events

The table below lists the events that wake the system from S3.

| Wake Event                  | Conditions/Remarks                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Button                | Wakes unconditionally from S3-S5.                                                                                                                                                                                                                                                                                                                                               |

| Onboard LAN Event           | Device driver must be configured for Wake On LAN support.                                                                                                                                                                                                                                                                                                                       |

| SMBALERT#                   | Wakes unconditionally from S3-S5.                                                                                                                                                                                                                                                                                                                                               |

| PCI Express WAKE#           | Wakes unconditionally from S3-S5.                                                                                                                                                                                                                                                                                                                                               |

| WAKE#                       | Wakes unconditionally from S3.                                                                                                                                                                                                                                                                                                                                                  |

| USB Mouse/Keyboard Event    | When Standby mode is set to S3, USB hardware must be powered by standby power source.<br>Set USB Device Wakeup from S3/S4 to ENABLED in the ACPI setup menu (if setup node is available in BIOS setup program).<br>In Device Manager look for the keyboard/mouse devices. Go to the Power Management tab and check 'Allow this device to bring the<br>computer out of standby'. |

| RTC Alarm                   | Activate and configure Resume On RTC Alarm in the Power setup menu. Only available in S5.                                                                                                                                                                                                                                                                                       |

| Watchdog Power Button Event | Wakes unconditionally from S3-S5.                                                                                                                                                                                                                                                                                                                                               |

# 7.3 USB Port Mapping

# 8 Signal Descriptions and Pinout Tables

The following section describes the signals found on SMARC<sup>®</sup> module's edge fingers. The pinout of the module complies with SMARC Specification 2.0.

The table below describes the terminology used in this section. The PU/PD column indicates if a pull-up or pull-down resistor has been used. If the field entry area in this column for the signal is empty, then no pull-up or pull-down resistor has been implemented. The "#" symbol at the end of the signal name indicates that the active or asserted state occurs when the signal is at a low voltage level.

## Note

Not all the signals described in this section are available on all conga-SA5 variants. Use the article number of the module and refer to the "conga-SA5 Options Information table" in section 1 to determine the options available on the module.

| Table 10 | Signal | Tables | Termino | logy | Descriptions |

|----------|--------|--------|---------|------|--------------|

|          |        |        |         |      |              |

| Term        | Description                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------|

| 1           | Input to the module                                                                              |

| 0           | Output from the module                                                                           |

| O OD        | Open drain output from the module                                                                |

| IOD         | Open drain input to the module, with pull-up on module                                           |

| OD          | Open drain                                                                                       |

| I/O         | Bi-directional Input/Output Pin                                                                  |

| PU(i)/PD(i) | Pull-up or pull-down resistor internal to the SoC or transceiver                                 |

| VDD_IN      | Signal may be exposed to module input voltage range (4.75 to 5.25V)                              |

| CMOS        | Logic input or output with 3.3 V signal level                                                    |

| GBe MDI     | Differential analog signaling for Gigabit Media Dependent Interface                              |